# Webinar: MMC- Technologies

Presenters: Juan Carlos Garcia and Farid Mosallat February 26 - 2015

### **Table of contents**

- 1. Modular multi-level converters

- 2. dq decoupled vector current control

- 3. Half and H-bridge converters

- 4. Detailed equivalent models of MMC valves

- 5. Simulation of a two-terminal system

- 6. Simulation of a dc-fault and re-start process (half- and H-bridge MMCs)

- 7. Setup of a three-terminal system (on-line demonstration if time allows)

- 8. Questions

# If you have questions during the Webinar

• Please e-mail PSCAD Support at

support@pscad.com

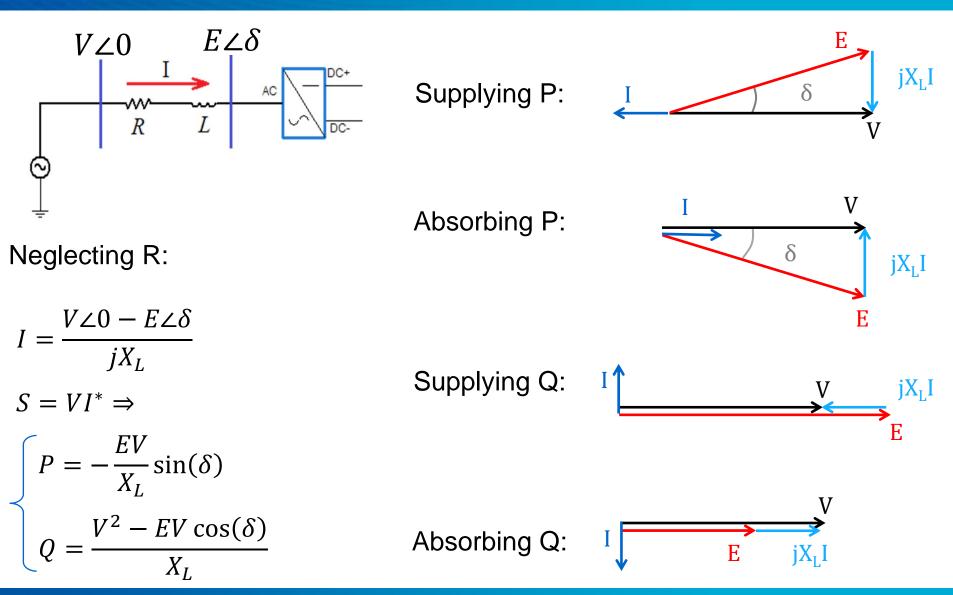

# **Grid-connected VSC: Operation principle**

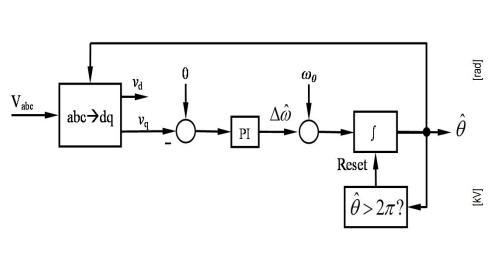

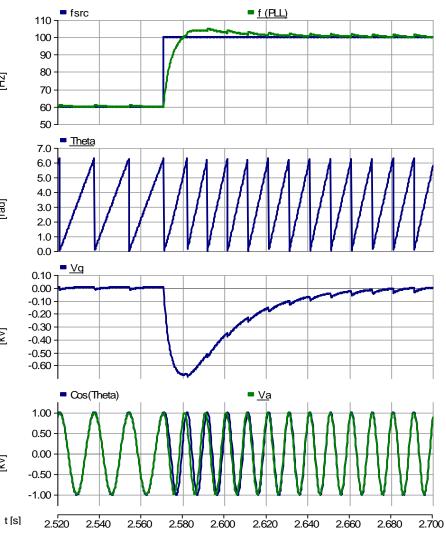

# Phase Locked Loop (PLL)

[Hz]

[k]

Extracting the phase angle of phase-A voltage

# Control modes for grid-connected operation

• θ

PLL

$V_{abc}$

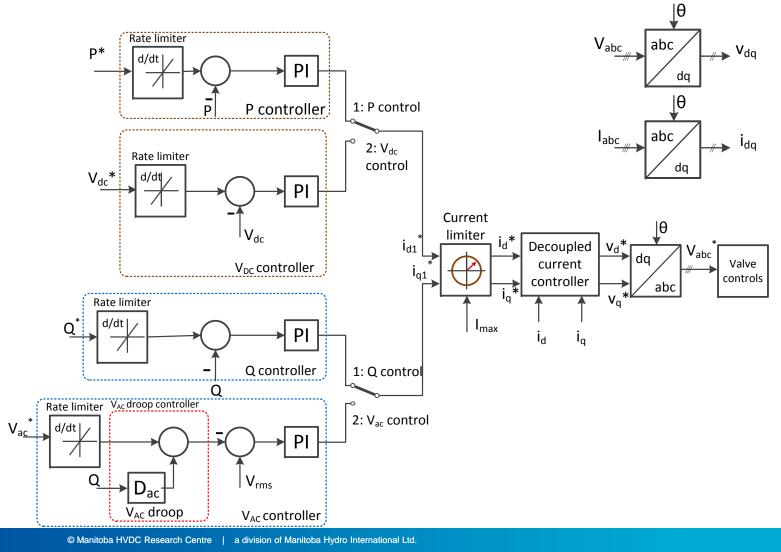

Basic control modes:  $(P/V_{DC})$ ,  $(Q/V_{AC})$

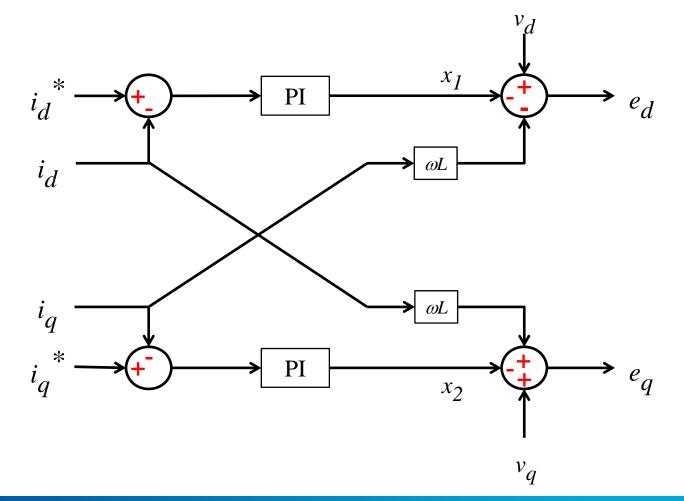

# Decoupled current control strategy

Current vector control with PLL locking to phase A voltage (cosine function)

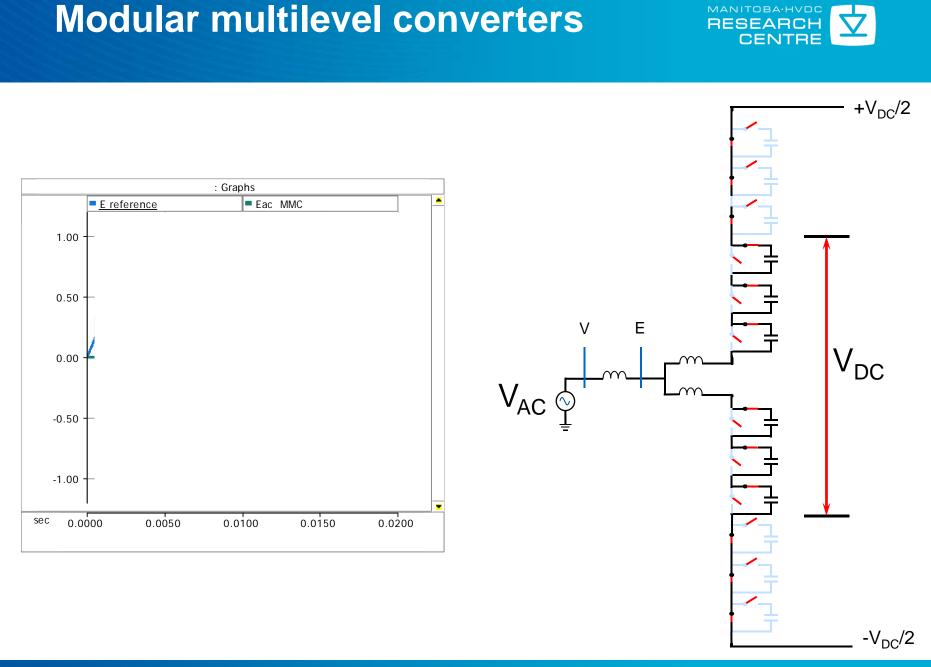

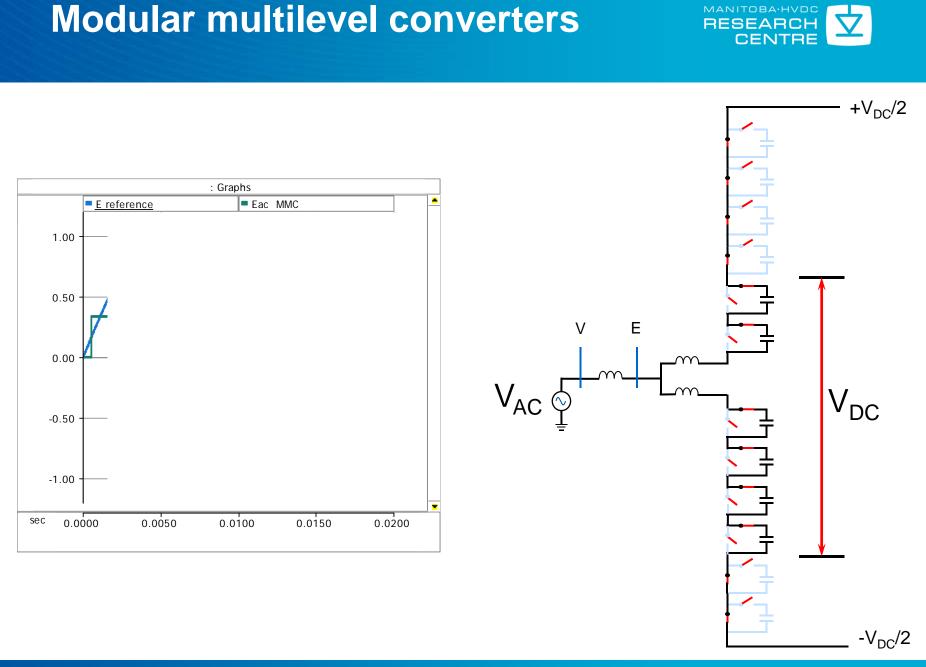

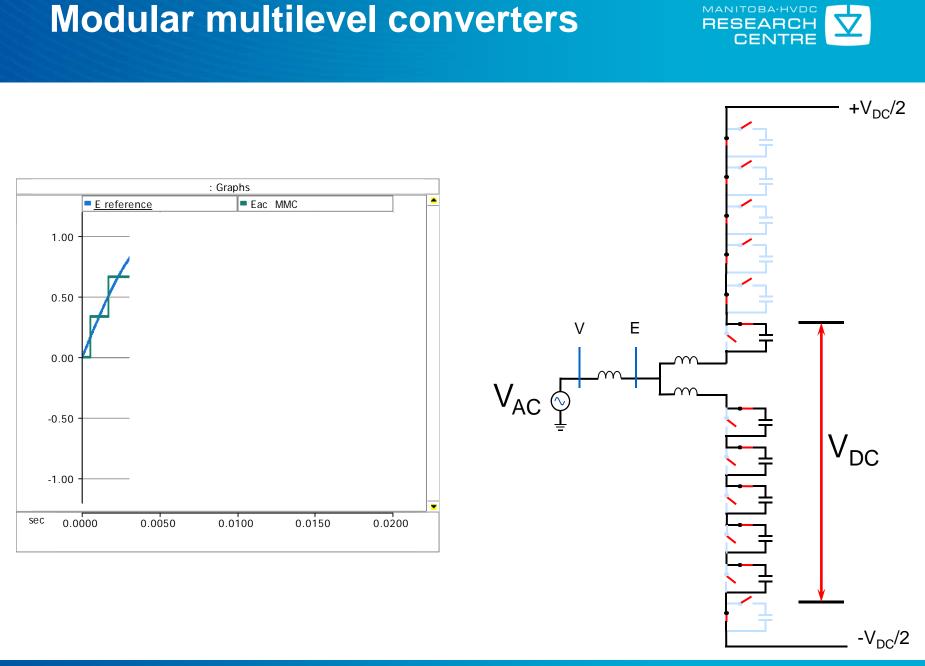

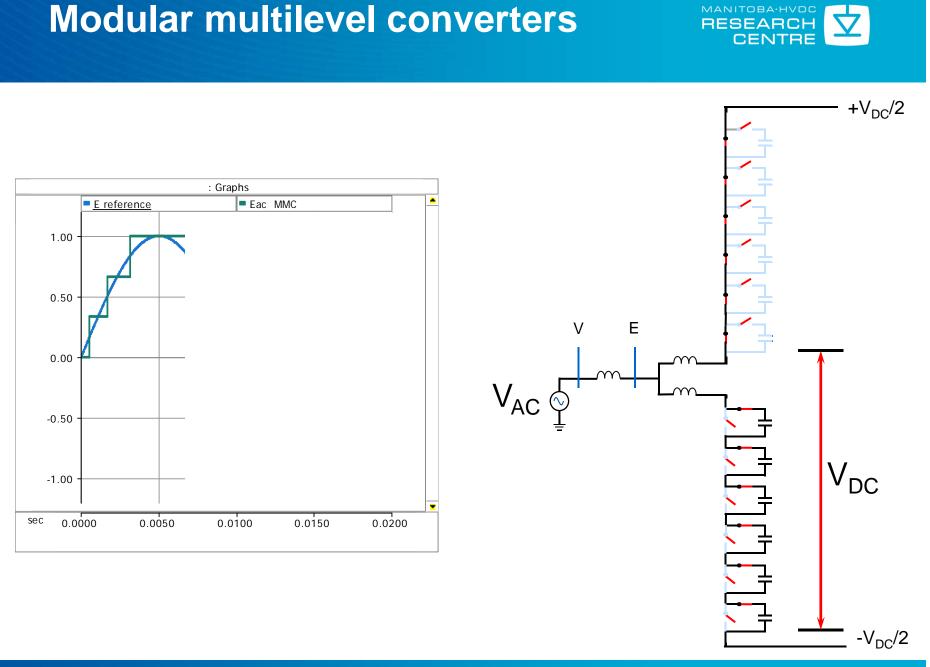

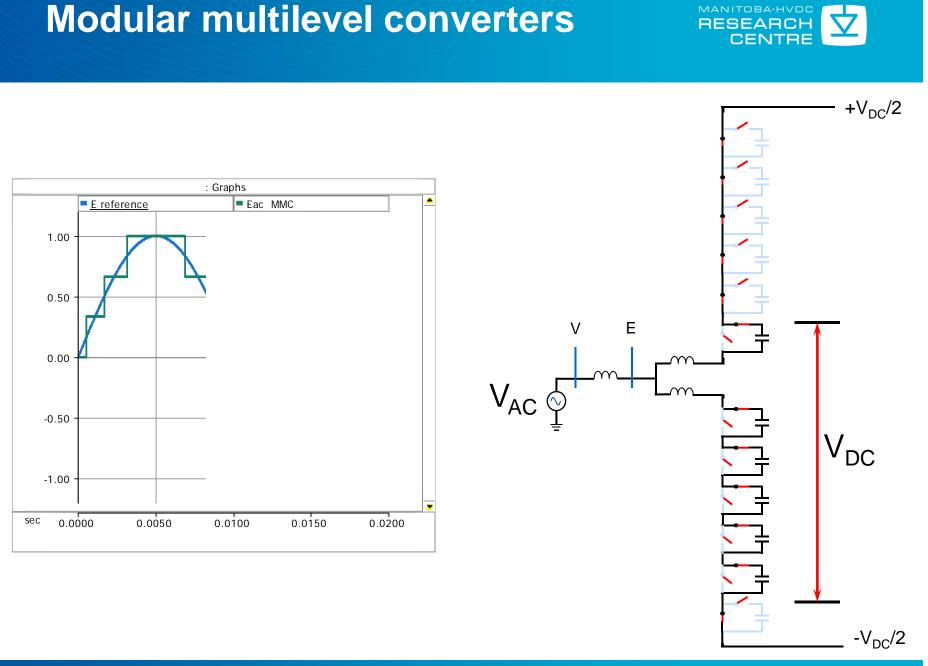

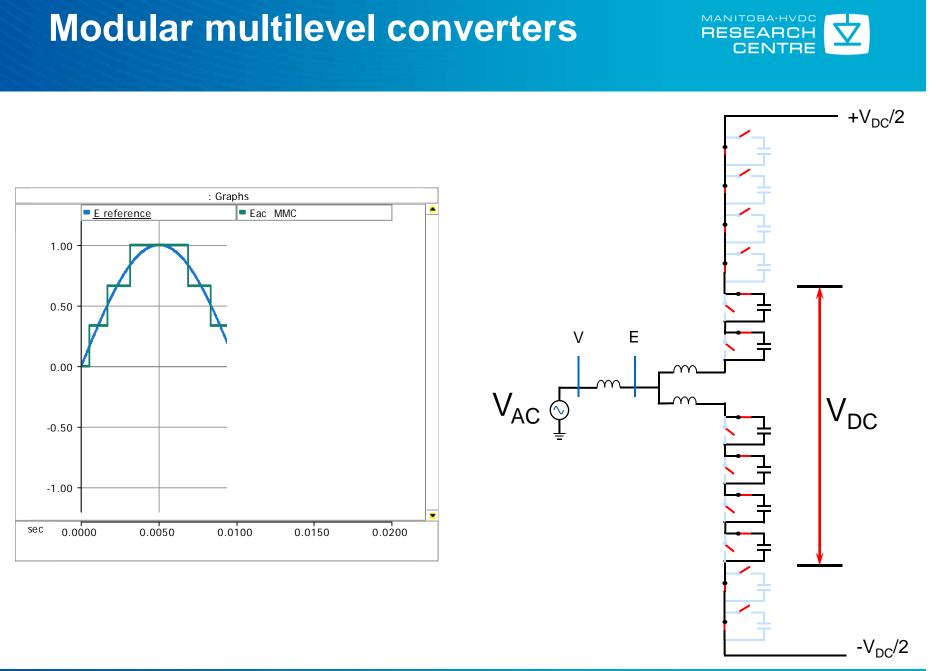

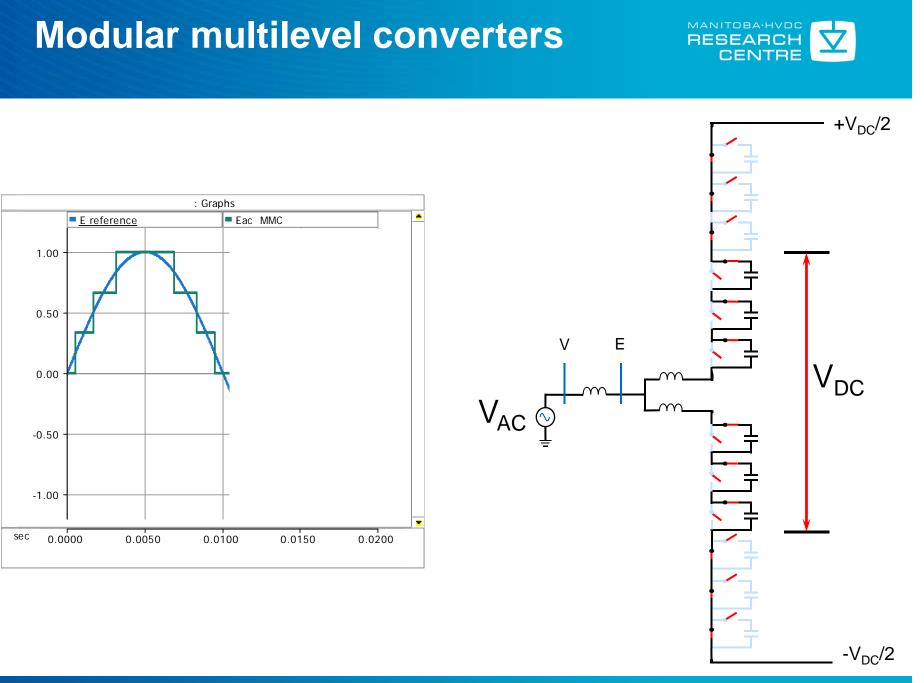

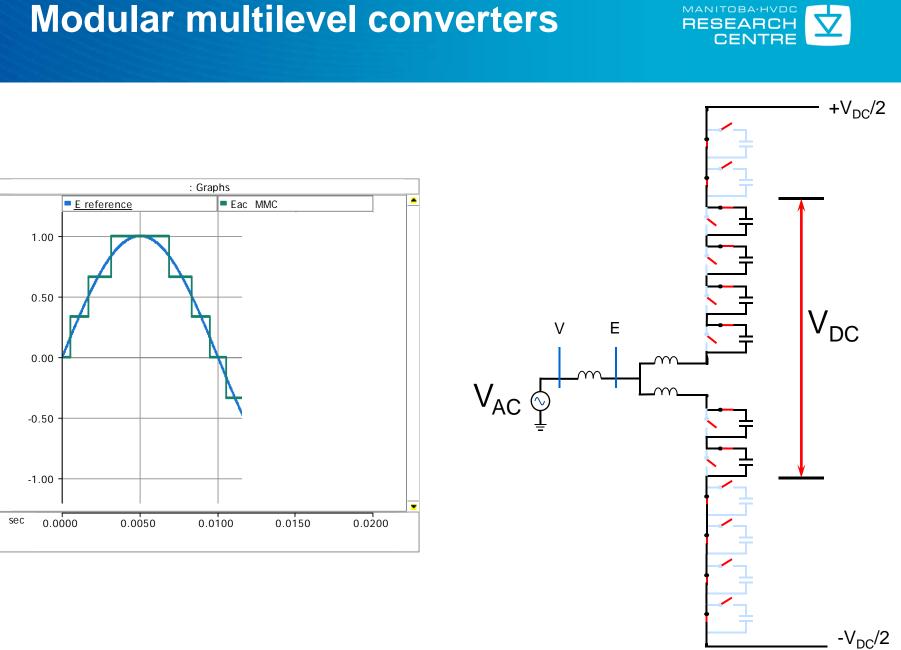

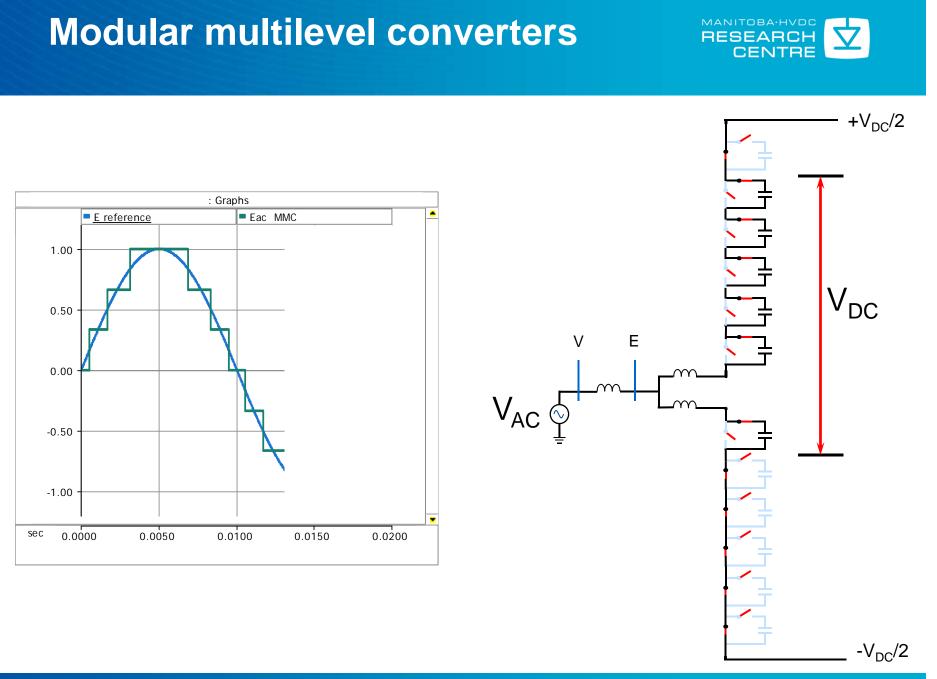

# **Types of MMC**

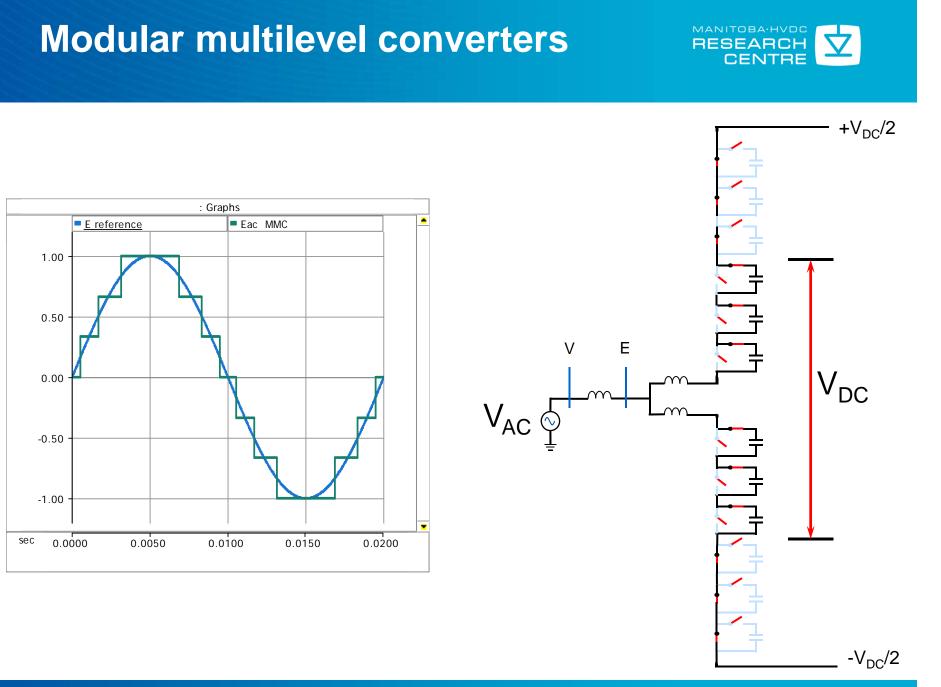

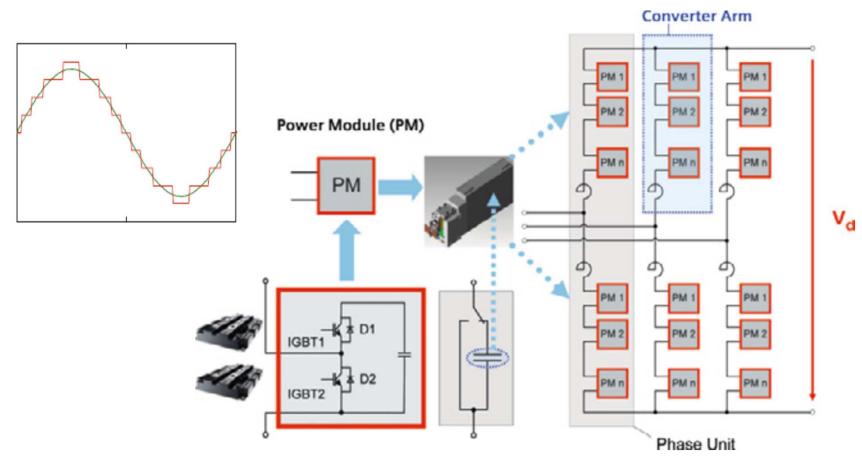

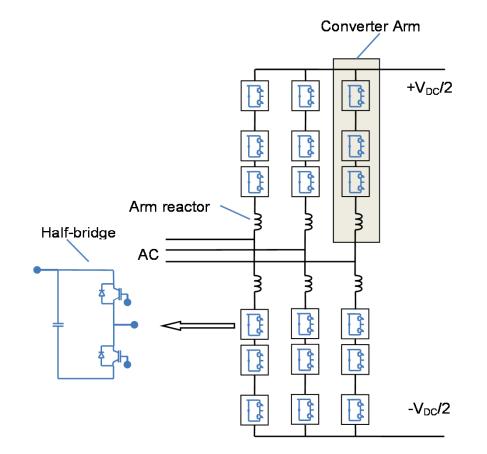

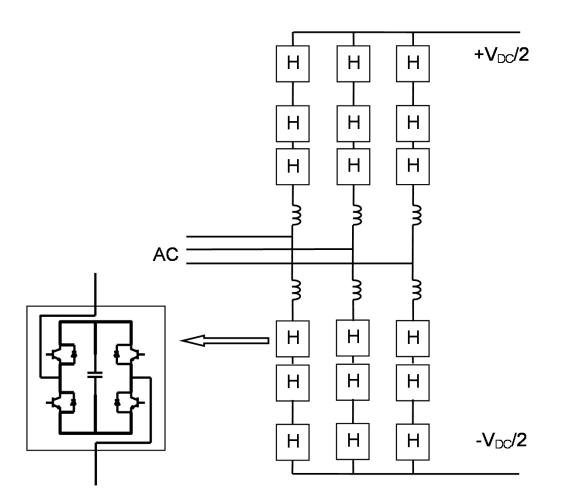

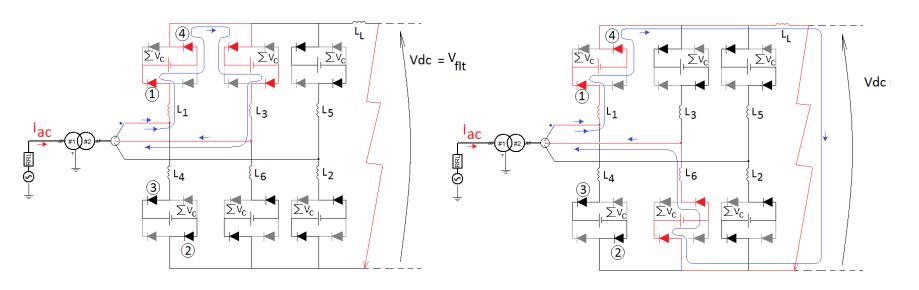

#### Half-Bridge MMC 2009

### Siemens diagram

Note: Filters not required

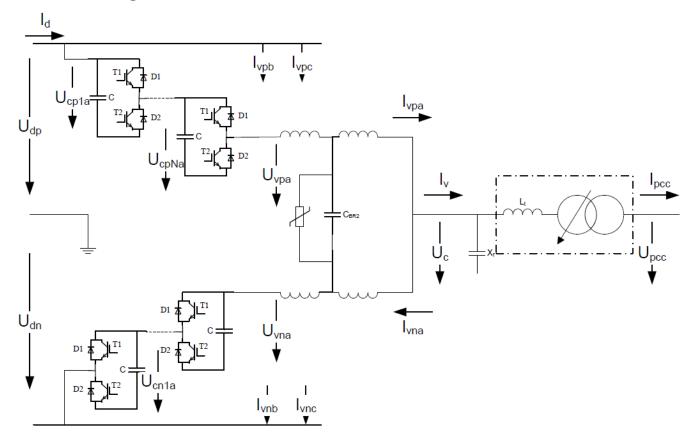

## **VSC Valves: MMC**

Half-Bridge – Cascaded 2-level converter

#### ABB diagram

## **VSC Valves: MMC**

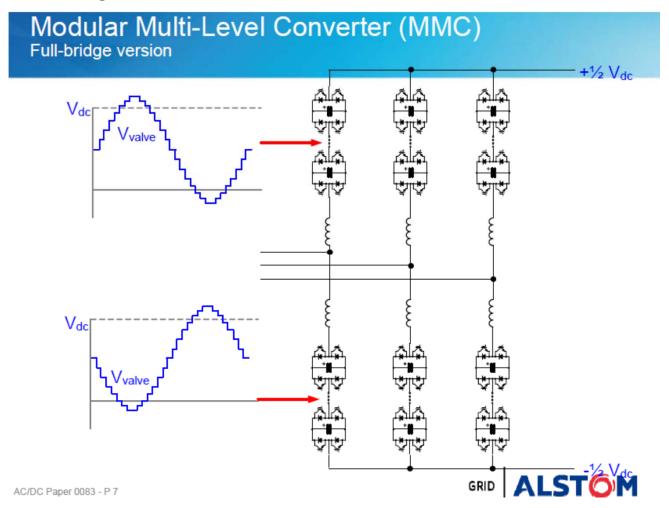

#### Full- or H-bridge cells

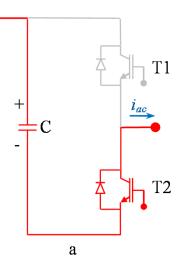

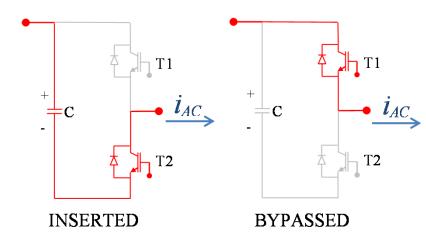

Three operating states in the half-bridge cell

| State description | Gates   |

|-------------------|---------|

| Insert +Vc        | (T2)    |

| Bypass capacitor  | (T1)    |

| Blocked           | None    |

| Forbidden         | (T1,T2) |

Note: Half-bridge CAN NOT generate  $V_{DC} = 0$

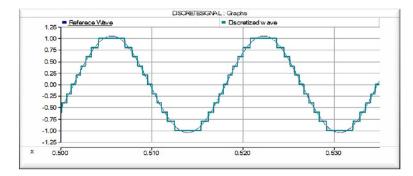

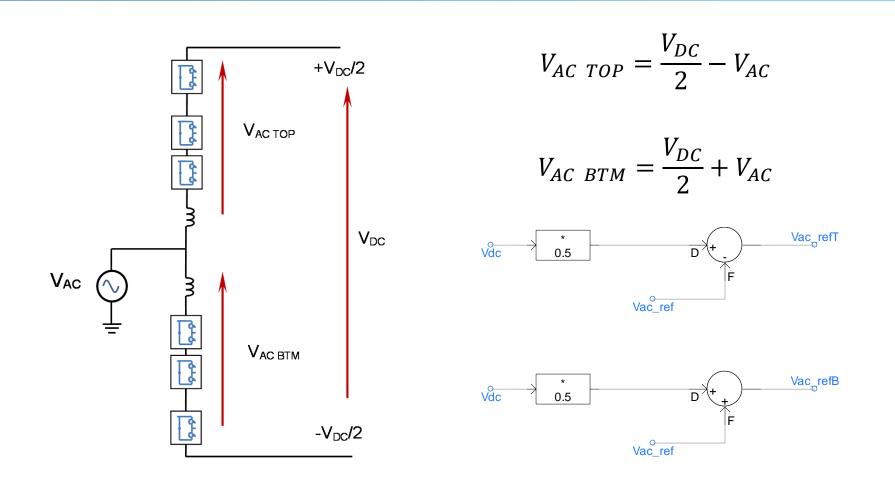

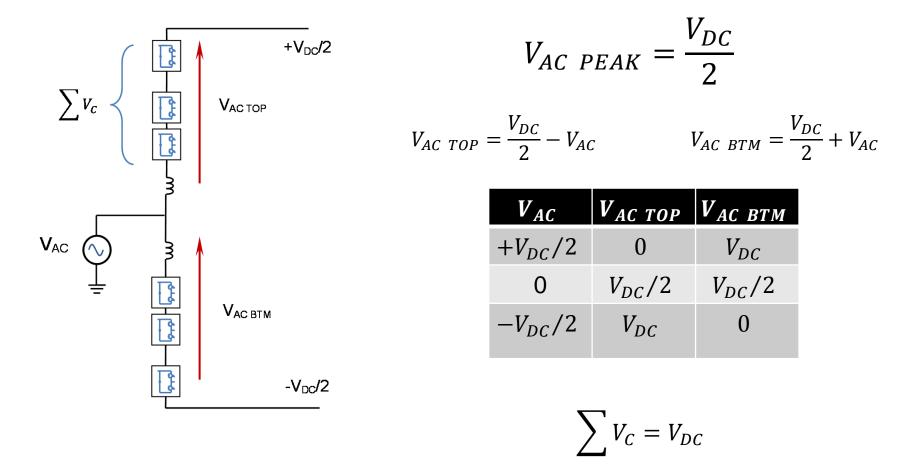

#### Assuming modulating index = 1

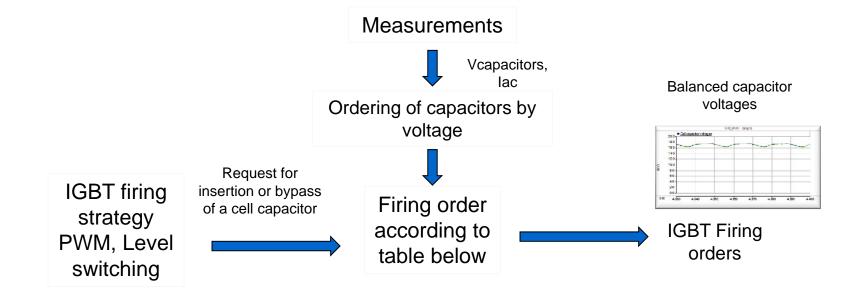

# Capacitor balancing: sorting method – Half-bridge cell

|                  | i <sub>ac</sub> < 0                  | i <sub>ac</sub> > 0               |

|------------------|--------------------------------------|-----------------------------------|

| Inserted cell    | Discharges capacitor                 | Charges capacitor                 |

| Bypassed<br>cell | Prevents discharging of<br>capacitor | Prevents charging of<br>capacitor |

# Capacitor balancing: sorting method – Half-bridge cell

| Action<br>requested | i <sub>ac</sub> < 0              | i <sub>ac</sub> > 0              |

|---------------------|----------------------------------|----------------------------------|

| Insert cell         | Insert cell with highest voltage | Insert cell with lowest voltage  |

| Bypass cell         | Bypass cell with lowest voltage  | Bypass cell with highest voltage |

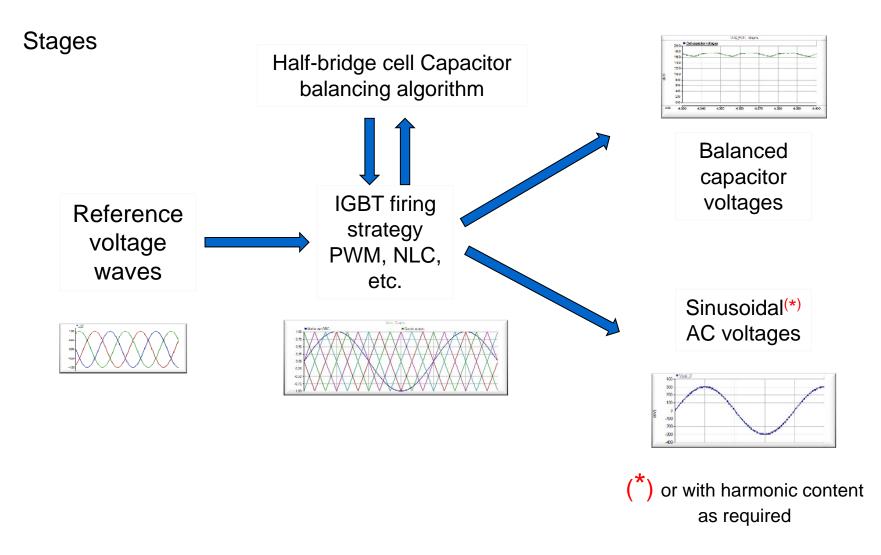

## **Low Level Controls**

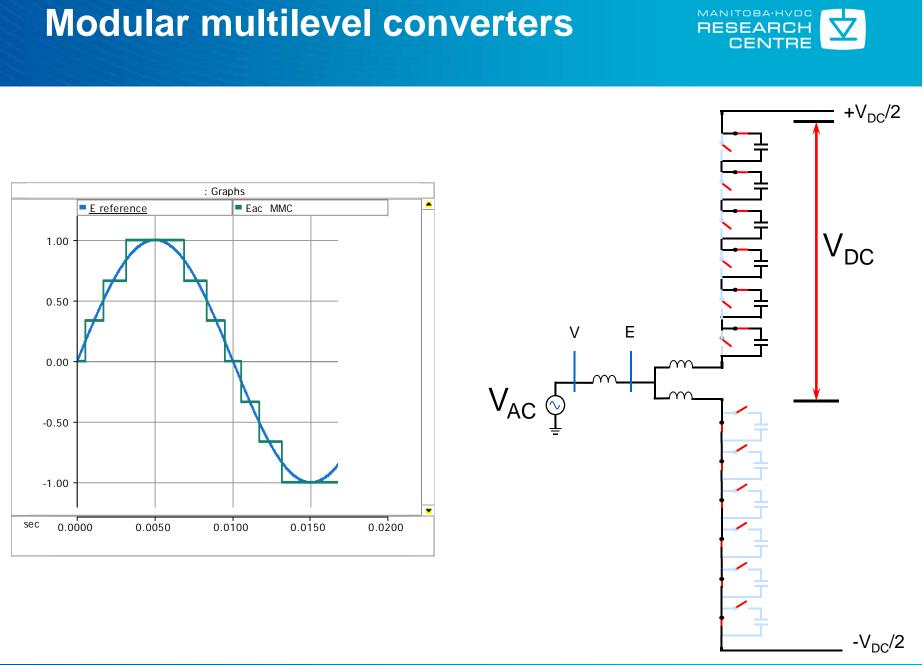

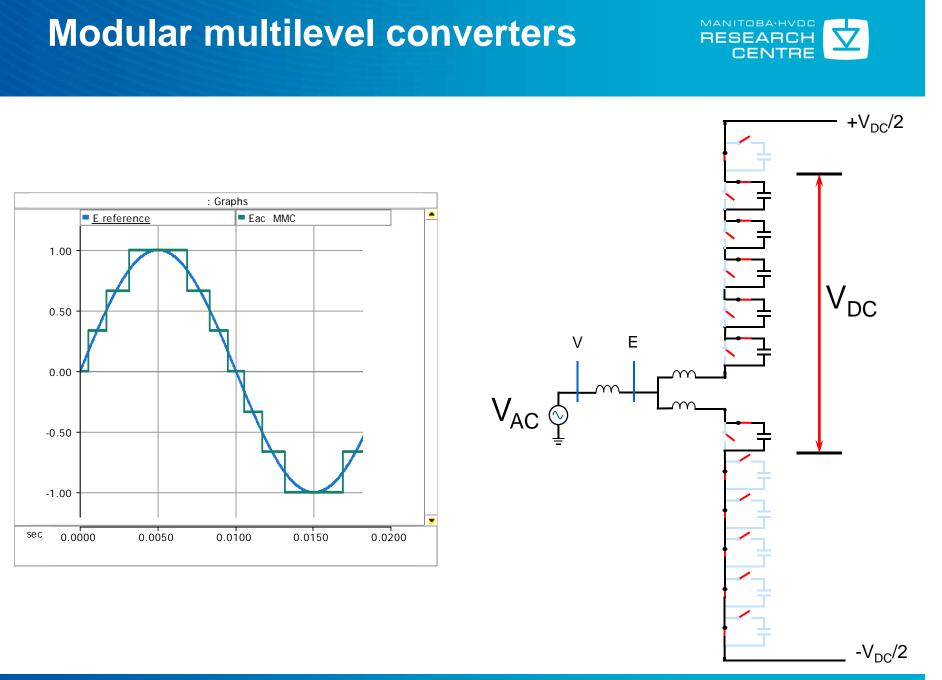

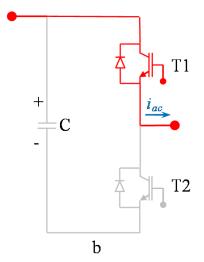

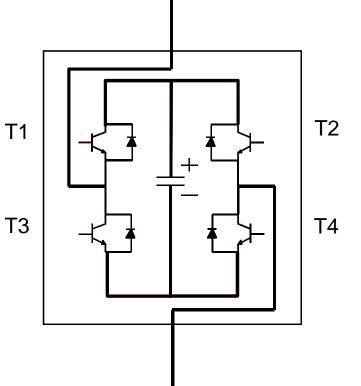

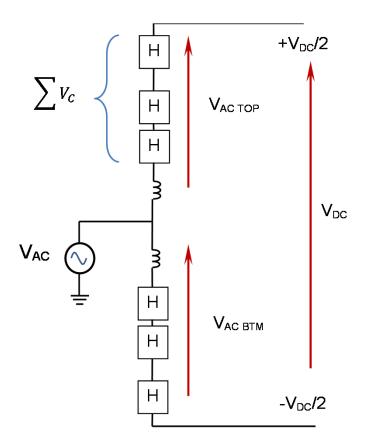

# H-bridge MMC (full-bridge)

#### Four operating states

| State description | Gates              |

|-------------------|--------------------|

| Insert +Vc        | (T1,T4)            |

| Insert -Vc        | (T3,T2)            |

| Bypass capacitor  | (T1,T2) or (T3,T4) |

| Blocked           | None               |

| Forbidden         | (T1,T3) & (T2,T4)  |

### H-bridge

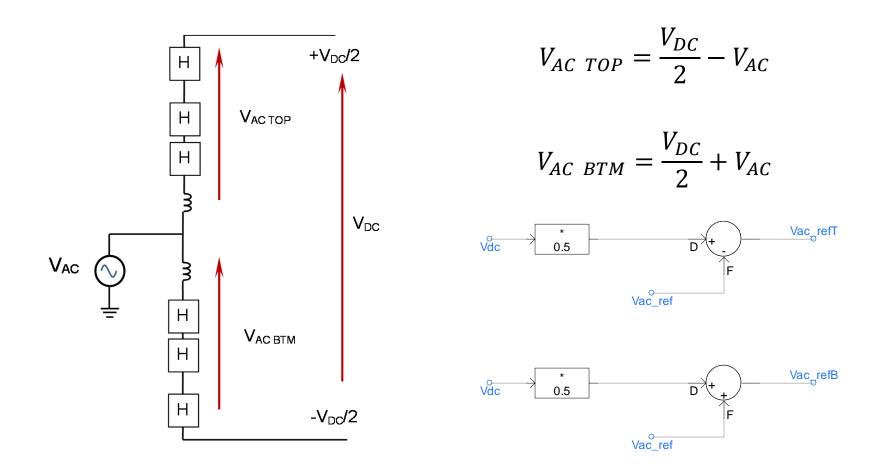

Note: H-bridge CAN generate  $V_{DC} = 0$

Assuming modulating index = 1.25

$$V_{AC \ PEAK} = 1.25 \frac{V_{DC}}{2}$$

$$V_{AC \ TOP} = \frac{V_{DC}}{2} - V_{AC} \qquad V_{AC \ BTM} = \frac{V_{DC}}{2} + V_{AC}$$

$$\frac{V_{AC} \ V_{AC \ TOP} \ V_{AC \ BTM}}{+1.25V_{DC}/2} = -0.125V_{DC} \qquad 1.125V_{DC}$$

$$+V_{DC}/2 \qquad 0 \qquad V_{DC}$$

$V_{AC}$  $V_{AC TOP}$  $V_{AC BTM}$  $+1.25V_{DC}/2$  $-0.125V_{DC}$  $1.125V_{DC}$  $+V_{DC}/2$ 0 $V_{DC}$ 0 $V_{DC}/2$  $V_{DC}$  $-V_{DC}/2$  $V_{DC}$ 0 $-1.25V_{DC}/2$  $1.125V_{DC}$  $-0.125V_{DC}$

$$\sum V_C = 1.125 \times V_{DC}$$

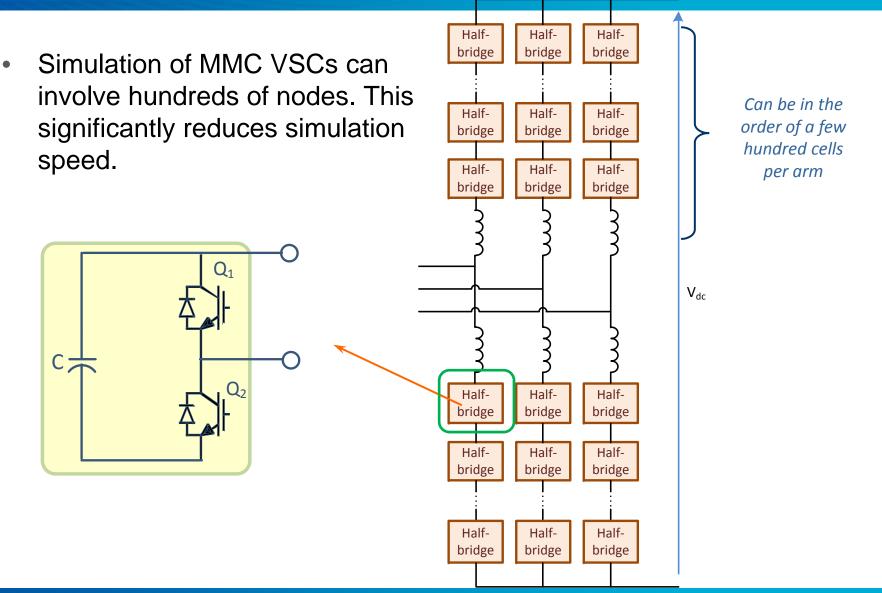

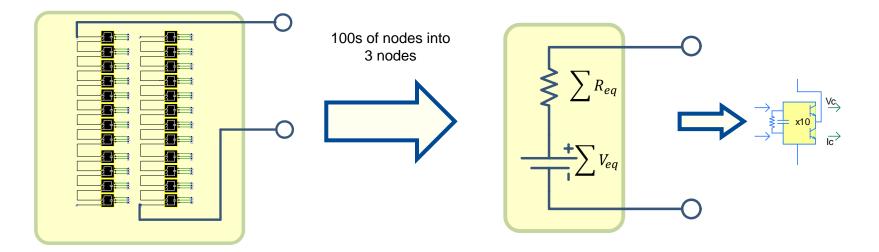

# Modelling techniques: MMC valves

# Modelling techniques: MMC valves

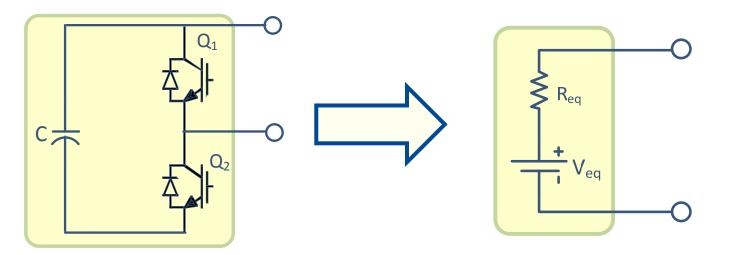

Using Thevenin equivalent: (detailed equivalent model)

$$R_{eq} = R_1 \left[ 1 - \frac{R_1}{R_1 + R_2 + R_C} \right]$$

$$V_{eq} = \frac{R_1}{R_1 + R_2 + R_C} V_C$$

U. N. Gnanarathna, A. M. Gole, and R. P.Jayasinghe, "Efficient Modeling of Modular Multilevel HVDC Converters (MMC) on Electromagnetic Transient Simulation Programs," IEEE Transactions on Power Delivery, vol.26, no.1, pp.316-324, Jan. 2011

## Modelling techniques: MMC valves

Using Thevenin equivalent: (detailed equivalent model)

$$R_{eq} = R_1 \left[ 1 - \frac{R_1}{R_1 + R_2 + R_C} \right]$$

$$V_{eq} = \frac{R_1}{R_1 + R_2 + R_C} V_C$$

- This type of model is identified in CIGRE WB B4-57 as model Type-4

- This model is good for system wide studies and for most DC fault simulations

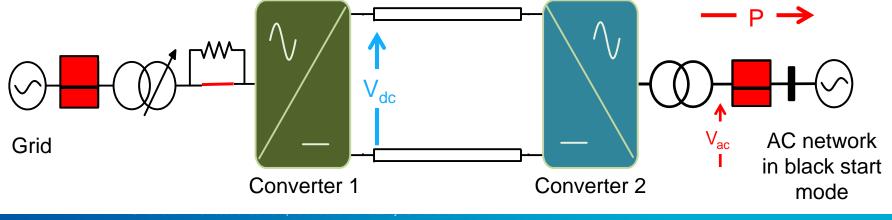

#### **Start-up sequence**

Converter 1: Grid-connected mode  $\rightarrow$  Controls V<sub>dc</sub> and Q (or V<sub>ac</sub>)

Converter 2: Grid-connected mode  $\rightarrow$  Controls P and Q (or V<sub>ac</sub>) – in black start

#### **Converter 1**

- Energize transformer & Precharge

- Bypass pre-insertion resistor

- Deblock converter 1

- Regulate V<sub>dc</sub>

mode

#### **Converter 2**

After V<sub>dc</sub> is regulated:

- Deblock converter 2

- Regulate V<sub>ac</sub>

- Ramp-up power transfer

#### **Start-up sequence**

• Sustained DC faults (unlike LCC)

- Most systems (except one) use cables:

- No need for fast re-energization

- Cables experience low occurrence of faults

- Fault clearing by opening AC breaker

- Most systems use cables:

- No need for fast re-energization

- Cables experience low occurrence of faults

- Fault clearing by opening AC breaker

## DC faults in VSC systems with Overhead Lines (OHL)

- High fault event frequency with OHL

- Need fast re-energization (re-closing) (400-500 ms) to prevent AC system movement

- DC breakers are required in order to achieve fast reenergization of DC system

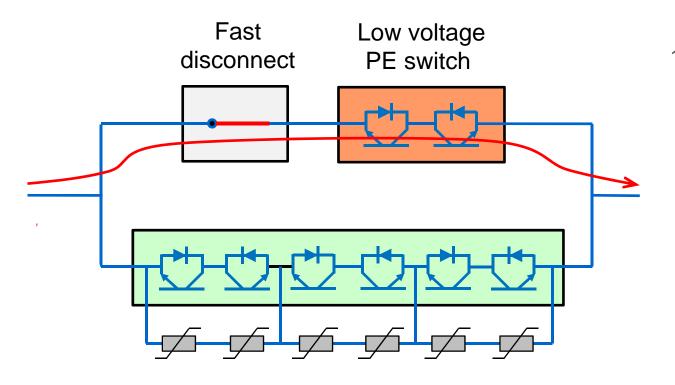

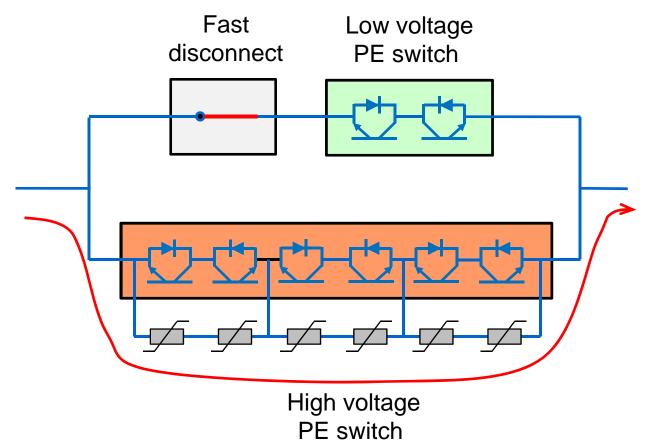

#### **DC-Breakers**

1. Overcurrent or DC fault under voltage front detected

High voltage PE switch

#### **DC-Breakers**

1. Overcurrent or DC fault under voltage front detected

RESEARCH

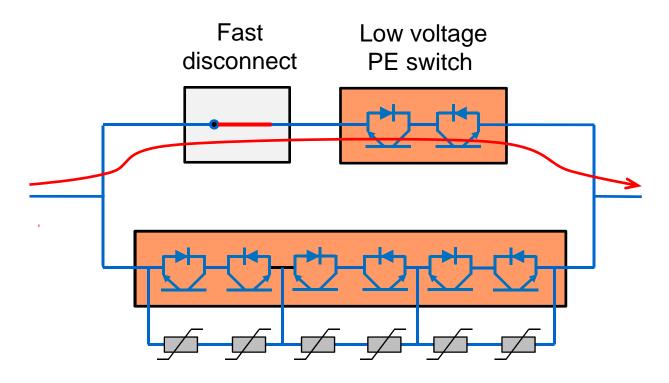

2. De-block HV PE switch

High voltage PE switch

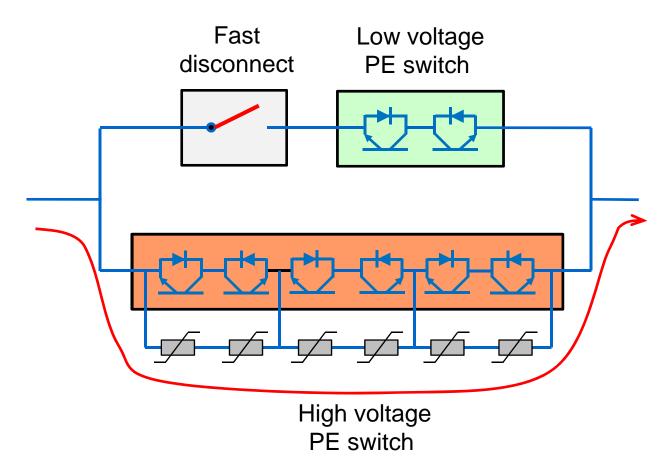

#### **DC-Breakers**

High voltage PE switch 1. Overcurrent or DC fault under voltage front detected

- 2. De-block HV PE switch

- 3. Open LV PE switch

#### **DC-Breakers**

1. Overcurrent or DC fault under voltage front detected

- 2. De-block HV PE switch

- 3. Open LV PE switch

- 4. Current transferred to HV PE switch

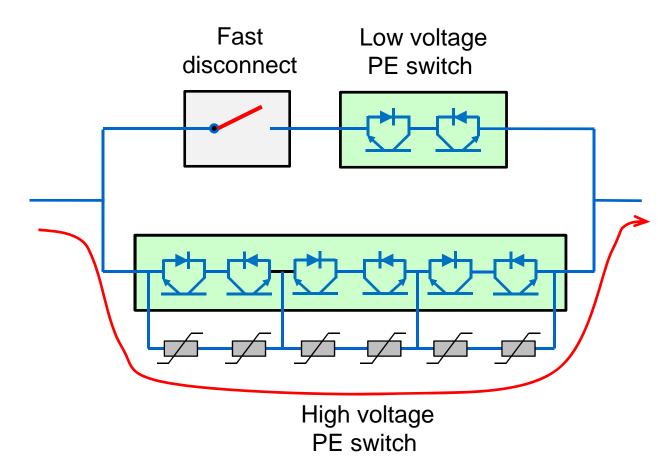

#### **DC-Breakers**

1. Overcurrent or DC fault under voltage front detected

- 2. De-block HV PE switch

- 3. Open LV PE switch

- 4. Current transferred to HV PE switch

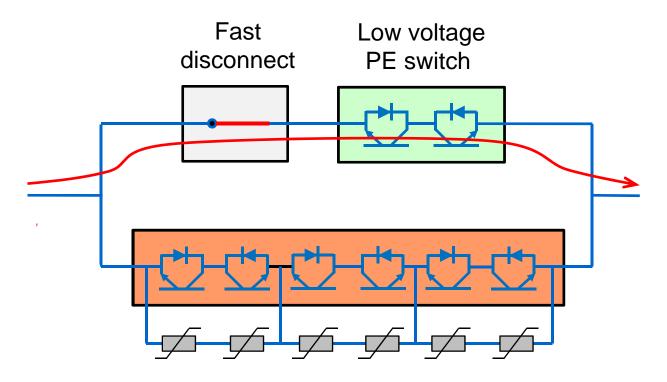

- 5. Open fast disconnect

#### **DC-Breakers**

1. Overcurrent or DC fault under voltage front detected

- 2. De-block HV PE switch

- 3. Open LV PE switch

- 4. Current transferred to HV PE switch

- 5. Open fast disconnect

- 6. Open HV PE switch

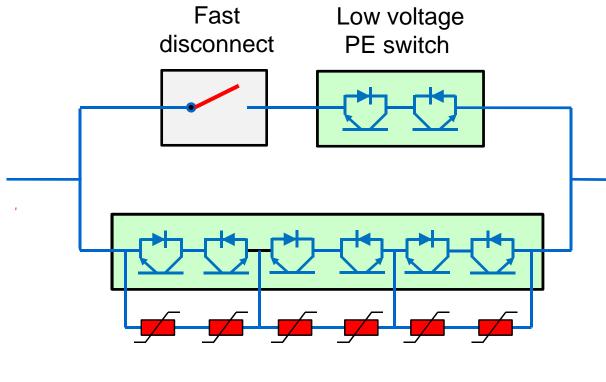

#### **DC-Breakers**

High voltage PE switch 1. Overcurrent or DC fault under voltage front detected

- 2. De-block HV PE switch

- 3. Open LV PE switch

- 4. Current transferred to HV PE switch

- 5. Open fast disconnect

- 6. Open HV PE switch

- DC current extinguished & energy dissipated in arresters

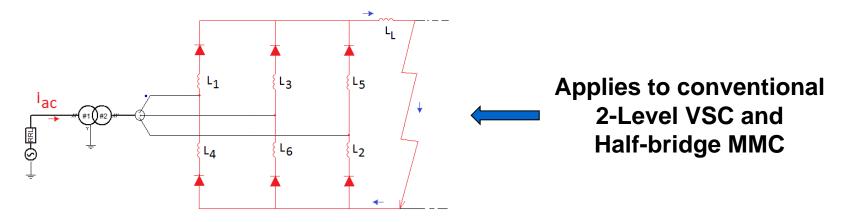

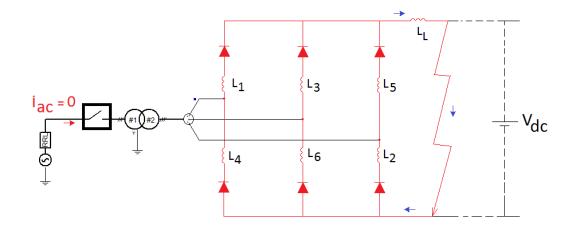

#### Fault clearance in H-bridge VSC systems (by blocking)

$$|i_{AC}| \begin{cases} > 0 \quad if \quad v_{AC \ l-l} \ge 2 \sum_{i} k_{i} v_{C} \\ = 0 \qquad otherwise \end{cases}$$

• Therefore lac=0 after blocking since

$$V_{AC_{L-L\,pk}} = m \sqrt{3} V_{dc}$$

$$\sum V_c = V_{dc}$$

$$m\sqrt{3} V_{dc} \ge 2 V_{dc}$$

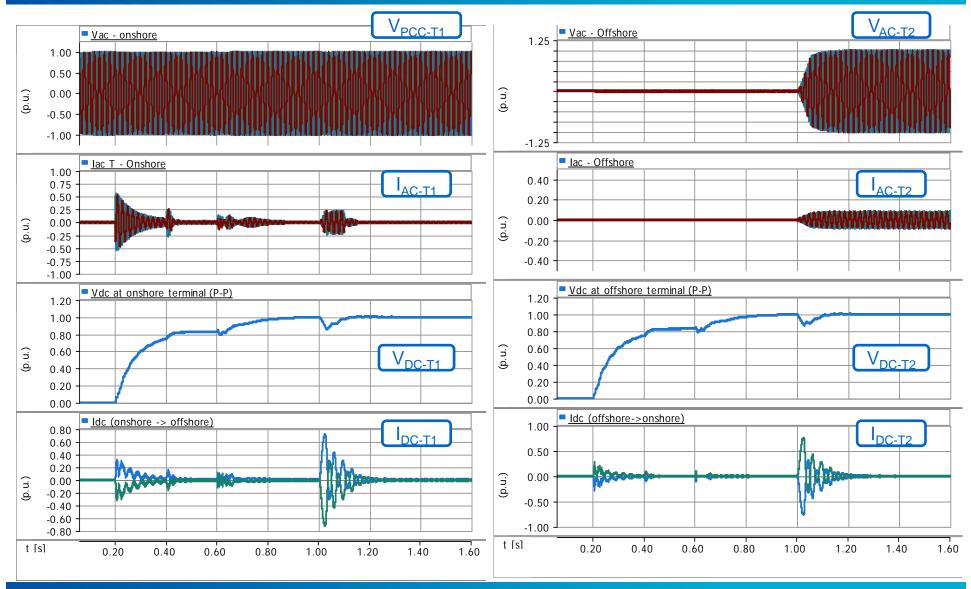

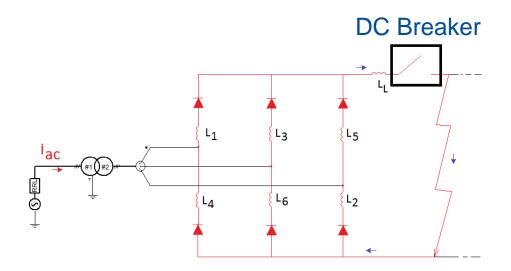

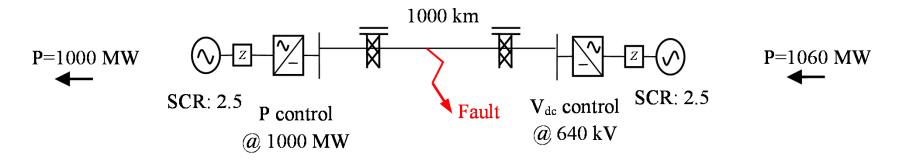

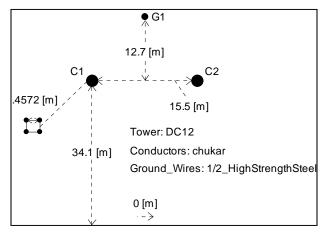

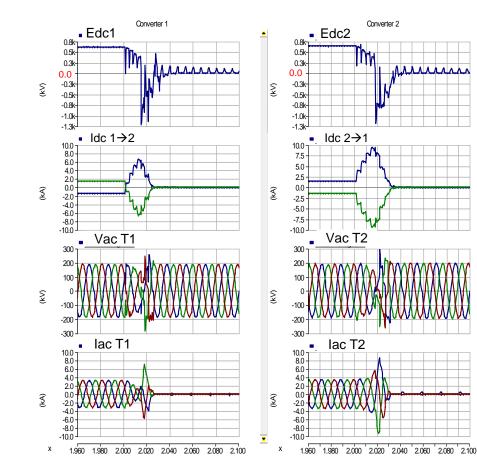

# Simulation of DC faults in a two-terminal system

#### **System description**

- T1: P control

- T2: Vdc control

- T1 & T2 in Vac control

TL Freq. dependent model

# Simulation of DC faults in a two-terminal system

## **DC Faults applied**

- At close and remote terminals

- Middle of the line

- Low impedance faults (0.1 ohm)

#### **DC Faults detection**

- Valve overcurrent (2.7 kA level)

- DC voltage drop (40% of diode rectifier voltage

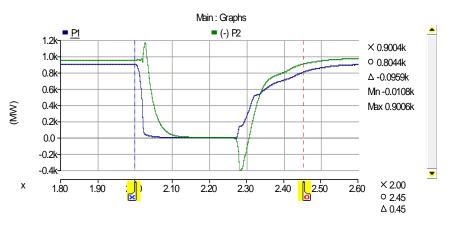

## Simulation of DC faults in a two-terminal system

- The total time to restore 90% power was 450ms

- Including 200 ms de-ionization time

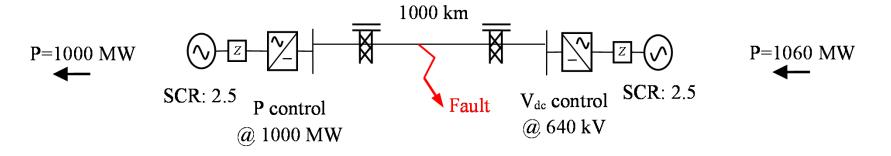

## Three-terminal system: Demonstration setup

- Starting with the two-terminal system from CIGRE B4-57

- If time allows

• Please e-mail PSCAD Support at

support@pscad.com